Software-Defined Radio Receiver: first signals!

I'm working on several projects in parallel. In addition to my "audio ARM-duino" (I need to give it a real name), I'm also working on a software-defined radio receiver. The primary goal is to keep the cost, size, and power consumption low and the spectrum coverage and bandwidth high. So I've been shopping around for highly-integrated receiver chips. Michael Ossmann of Great Scott Gadgets pointed me toward the ADRF6850. It's got an integrated variable-gain amplifier (VGA), quadrature mixer, and a PLL/VCO for tuning across a 100MHz - 1GHz range. You put an RF signal in, and you get baseband out. Nice.

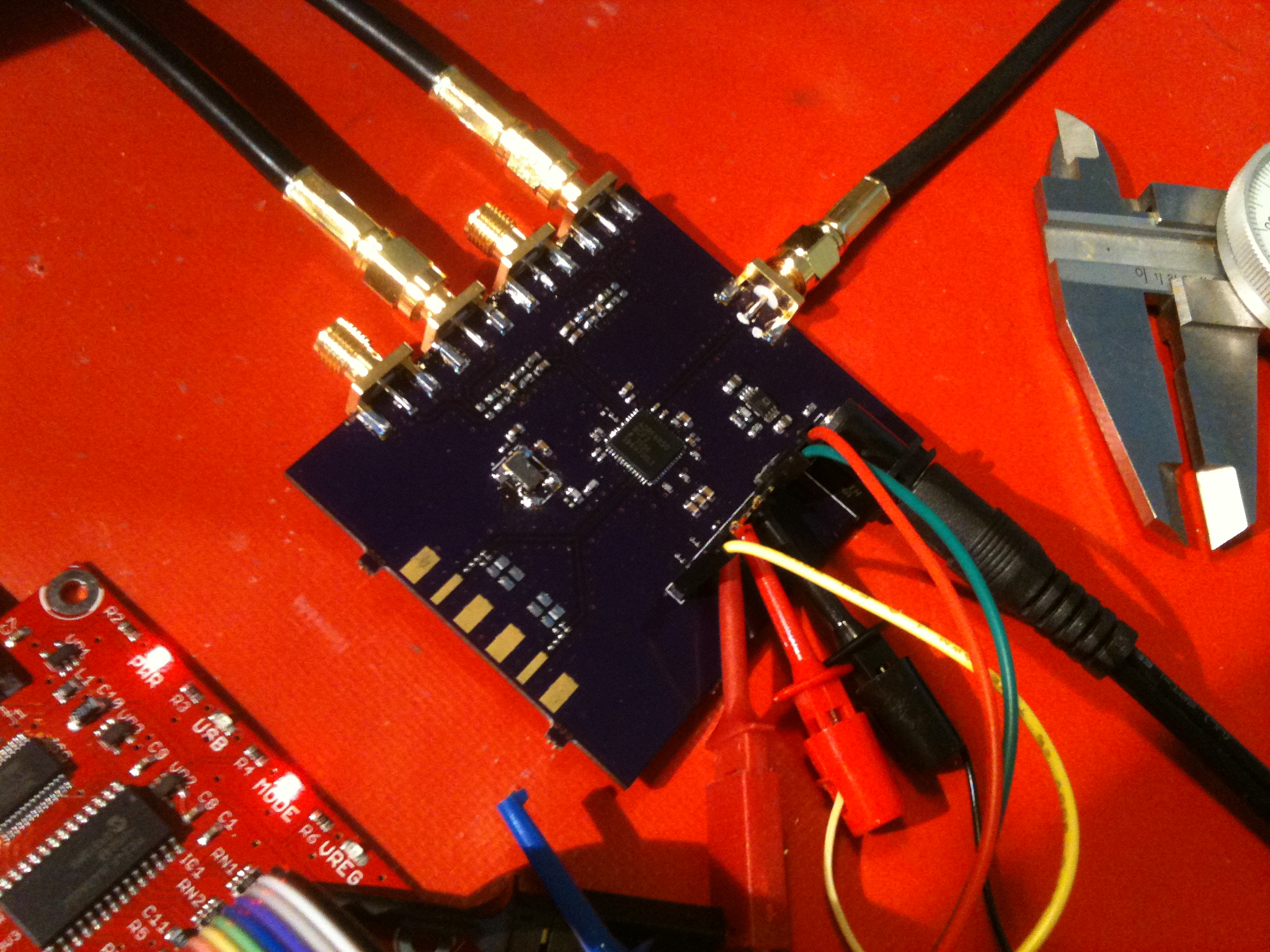

I designed a breakout board and had it made via Laen's PCB order. Last night, I soldered it up, and this morning I started working with it through the I2C interface, using my Bus Pirate. By the afternoon, I was receiving pager signals at 929.675MHz, and aviation voice signals in the 118-137MHz band.

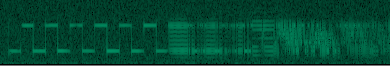

Here's a POCSAG pager data burst. You can see the preamble as a square-ish zig-zag at the left side (start) of the burst:

For the aviation audio signals, all I had to do was amplitude demodulate the quadrature data (which I captured with my computer's stereo audio input). Treat the quadrature sample pairs as complex numbers (which they are…), compute the magnitude of the complex vector, bandpass-filter the result, and you have the original audio!

Comments

This chip looks fantastic! I hadn't heard of it before and I can't see it on Analog's site through the "RF / IF ICs" section it lives in unless I search for the part name directly! How did you come across it? Have you mostly followed the reference design with your board?

Is this the beginnings of the next DIY product from ShareBrained?! :)

Given the response at DEF CON last week, I'm thinking so! I had no idea so many people are in to software-defined radio.

@joel,

I'm not sure where I heard about it, but it may be in one of the RF-newsletter e-mails that Analog sends me from time to time. Or Michael Ossmann (the Ubertooth guy) might've pointed it out to me. In any case, it seems like a perfect recipe for an inexpensive software radio receiver.

Yes, my design isn't all that far from the reference design. However, in the next week, I intend to do a complete stand-alone design. Right now, my plan is to integrate the ADRF6850 with an ARM Cortex-M3 microcontroller. The ARM will sample the quadrature baseband outputs, through a low-pass filter, at 2MSPS. That should leave me with maybe one 1MHz of useable bandwidth. Then the ARM will demodulate or downsample that data and send it over full-speed USB. Optionally, I might support a battery and LCD to make the device entirely stand-alone and portable. Sound cool? Let me know what you think…

SDR is all the rage in amateur radio at the moment. Most of the interest in in transceive operation, of course, but this is exciting. Will watch the progress closely!!

Jared, You demo'ed your rf6850 front-end based SDR to me in the HHV at DEF CON last week. I must admit, I am looking forward to your M3 based standalone. Sound cards are great for most things, but we all need more bandwidth!

Thanks again :)

@Lance: I hope to have something to show soon. The next DorkbotPDX four-layer board order goes out on Monday, and I hope to have a prototype combined RX + ARM + USB design in there. Two weeks later, I should have a built prototype. Expect more news then!

@Bart: I would love to do a transceiver someday, but for now, I'm really trying to keep the cost (and power consumption) down. I also doubt that this single-IC solution will have the sensitivity that amateur radio people would desire. I'm seeing this as more of an spectrum exploration device – find a signal and see what it contains. There's a lot of interesting stuff in the 100MHz to 1GHz range. A metaphor I've been thinking about is Geordi La Forge's electromagnetic visor in Star Trek: The Next Generation. This radio would provide great insight into the signals around you.

I've spent the last year and a half designing receivers for a wildlife radio tracking system and am keen to see if this chip will be sensitive enough so that I can throw all of that out. I bought the evaluation board, which arrived yesterday, and am trying to suss out the i2c interface right now.

I look forward to seeing the next evolution of your project! If the chip is suitable, I plan to use four in conjunction with a high speed (65 MSPS) four channel ADC (LTC2172) and a Xilinx Spartan-6 for signal processing and gigabit Ethernet duties. These bits are already working, at least. It's fundamentally the same as yours, except that I need more channels and wider bandwidth! :)

@Joel: multiple 65MSPS ADCs and an FPGA – sexy! I am curious though why you have only four ADC channels to sample from four ADRF6850s. Don't you want to sample the quadrature output on each? Or perhaps you're doing downconversion to a low IF? If so, I think I've seen some other highly-integrated chips that might work even better for you. Perhaps the [https://estore.rfmd.com/RFMD_OnlineStore/Browse.aspx?Family=Integrated%20PLLMixers rel="nofollow">RFMD RF2052, RF2053, RF2056, or RFFC2072</a>?

I aspire to build a software radio with that amount of bandwidth. I hope to get there sometime next year. I do have a prototype right now (using separate mixer and VCO+PLL ICs) that involves the most amazing ADC on the market – the [http://www.analog.com/en/analog-to-digital-converters/ad-converters/ad9262/products/product.html" rel="nofollow">Analog AD9262</a>, a sigma-delta ADC for RF applications. The prototype is right now just fiberglass. I got the schematic and PCB design done and built, but haven't developed the cojones to solder $100 worth of parts to it yet…

If you're publishing your progress somewhere, please share! I'd love to keep track of your progress and chime in occasionally if I have any insight to offer.

Yeah, I'll take credit for pointing you toward the ADRF6850. We talked about it in Seattle. Now I just need to get working on my designs too. . .

@mossman: My apologies. I have updated my post to give you proper credit.

I'm trying to detect wildlife transmitters that are just pulsed CW, so I'm not sure there's enough to be gained from IQ sampling to justify an extra expensive ADC. I haven't really made up my mind about low IF or baseband sampling - either should work for my application with such a fast ADC.

You're very welcome to check out my research blog at http://tumblr.tristesse.org/ ! I've also conducted some additional tests on the ADRF6850, the results of which are at http://tristesse.org/20110822 and http://tristesse.org/20110823 . Any input or thoughts would be appreciated :)

This evening we did some additional preliminary tests today to check the stability of the PLL - I want to have four perfectly synchronised receivers so I've set the LO to 150 MHz and fed in a 150 MHz RF signal and looked at the (DC coupled) baseband. Unfortunately the results aren't very encouraging - it jumps all over the place, even when I use an OCXO-powered function generator as the REFIN clock :( The next step will be to try a much higher frequency REFIN (it goes up to 300 MHz). If that's no good, I may have to revert to passive mixers and a single DDS for the LO.

The RFMD parts look really interesting though, thanks for pointing them out! I'm not sure I've even heard of RFMD before. I just wish they had a four mixer model too. I'll have a better look at them tomorrow.

Don't be too scared about soldering expensive components. Free samples and a cheap hot air tool from eBay, and you won't be afraid of any part!

Scratch that - I've decided that it has a really good PLL! The function generator just wasn't very stable. Now I'm using a 10 MHz OCXO ($10 on eBay) directly and by twiddling tuning knobs, can get it perfectly in sync with another free-running oscillator for around thirty seconds. What a chip! :) I just wish it didn't take 330 mA. The RFMD ones are much lower power, even though you have to use an external gain block.

Anyway, looking forward to hearing what you do with yours next!

Check out http://openhsdpr.org/ if you haven't already :) Also, http://www.funcubedongle.com/

ADRF6850 seems like a pretty nifty little chip!

Could this potentially be used with ATPDEC to decode weather satellite images? http://atpdec.sourceforge.net/

@Joby: I'm checking out what's required for an antenna. Assuming I don't need to build anything insanely complicated to get a strong signal, I might give it a shot tomorrow! I think signal strength will be the only issue for the device I've built – the front end is wide open at present, meaning I get a lot of FM band noise in my baseband. I can filter it out, but I suspect it's still going to impact overall sensitivity for nearby signals.

@Joby: I just wrote a post about using my radio to receive APT signals from NOAA POES satellites. It worked surprisingly well, despite my terrible antenna and my wide-open (unfiltered) receiver front-end:

http://www.sharebrained.com/2011/09/06/signals-from-space-part-1/

Do you already know which ADC you are going to use for the M3 version?

@Ulf: My hope is to use the internal ADCs on the STM32F205. They're 12 bits each, and there's three of them. They can be configured to sample in a staggered manner, giving up to 6MSPS rate in a single channel. They can also be used separately to capture two channels (quadrature) at 2MSPS. Quadrature simplifies the math a bit, which is important if I'm going to have the Cortex-M3 doing a lot of demodulation signal processing. So for now, I'm aiming for a quadrature solution using two ADC channels. Realistically, I should be able to provide up to 500kHz of usable bandwidth. The big challenge I'm working through now is the gain structure. I was using my laptop's audio input to sample the baseband from the ADRF6850. The baseband noise floor is below -90dBFS, so I'd need to amplify significantly (at least 40dB, I'm guessing) to use the 12-bit converters in the STM32F205. In a perfect world, the chip I'm using would have variable gain on the baseband side of the mixer.

Ok, so you are using a transformer or op amp to convert both outputs to single ended signals and than sample these with the STM32. I thought you might use an external ADC with differential inputs. But of coarse you plan to use the internal ADCs of the STM32 is not so expensive.

@Ulf: Right. I was planning to use op-amps as difference amplifiers to convert differential to single-ended, and also boost the signal a bit, since it's not strong enough to sample with the ADC. However, I'm quickly realizing that my design isn't all that much better than a Funcube Dongle – mine would be a bit cheaper, and would offer more bandwidth, but I'd be limited to tuning 100MHz to 1GHz. The ADRF6850 also consumes a massive amount of power, which would mean I couldn't run from USB power, and if I wanted to run from batteries, I'd need a lot of batteries, or I'd need to charge them all the time… So I'm back to the drawing board…

Yikes, I'm half-way through building a few prototype receivers and the ADRF6850 is practically out of stock everywhere but directly from Analog, who have a 100 part minimum!

@Joel: That's no good. I see Digi-Key has two. I might have one or two samples laying around that I may not use (in the near term, at least). And you should also know that Digi-Key may say "out of stock" or even "non-stock" for some stuff, but you can still order it, and they'll still get it for you. The date Digi-Key states for ordering more ADRF6850s is December 6th. So if you order now, you can have 'em in two weeks, maybe?

I think Digikey's stock count isn't quite live, because I'd already bought those two at great expense :( I've never quite trusted their shipping dates - when Spartan-6 FPGAs were not yet released, their ETA on them was perpetually a few weeks in the future! All other distributors are a bit less optimistic, giving 12 weeks. I've ordered another couple of samples for now as well, so that should be enough to give me one and a half working prototypes (each has four chips).

I suspect your series of articles has whipped up strong world-wide demand for these parts :D